SN75DP139

SLLS977F - APRIL 2009 - REVISED JULY 2017

# SN75DP139 DisplayPort to TMDS Level-Shifting Re-Driver

#### **Features**

- DisplayPort Physical Layer Input Port to TMDS Physical Layer Output Port

- Integrated TMDS Level-Shifting Re-driver With Receiver Equalization

- Supports Data Rates up to 3.4 Gbps

- Achieves HDMI 1.4b Compliance

- 3D HDMI Support With TMDS Clock Rates up to 340 MHz

- $4k \times 2k$  Operation (30 Hz, 24bpp)

- Deep Color Supporting 36bpp

- Integrated I<sup>2</sup>C Logic Block for DVI/HDMI Connector Recognition

- Integrated Active I<sup>2</sup>C Buffer

- Enhanced ESD: 10 kV on All Pins

- Enhanced Commercial Temperature Range: 0°C to 85°C

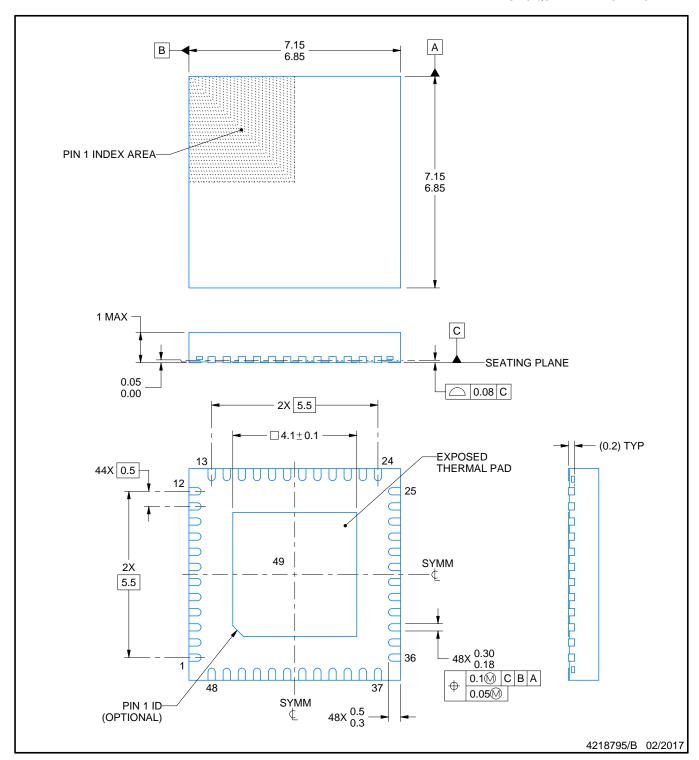

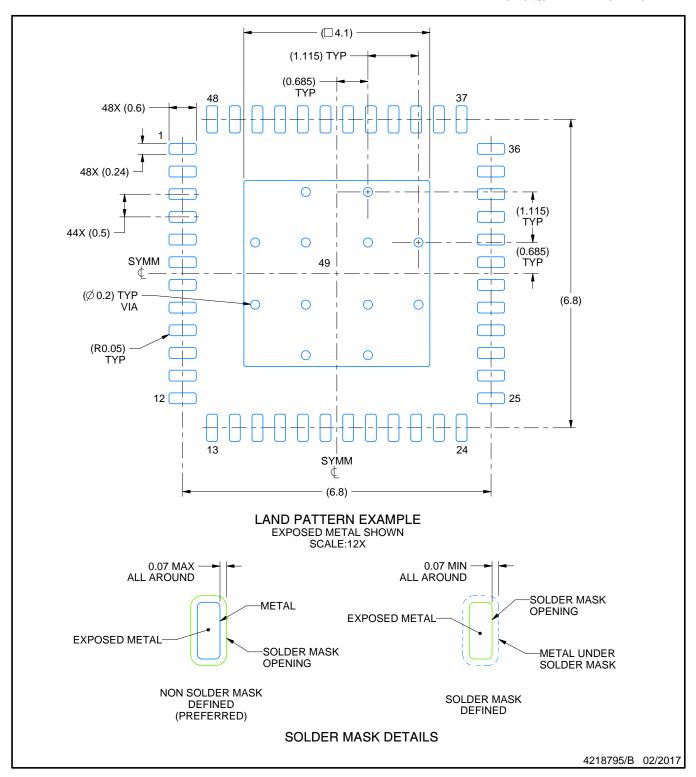

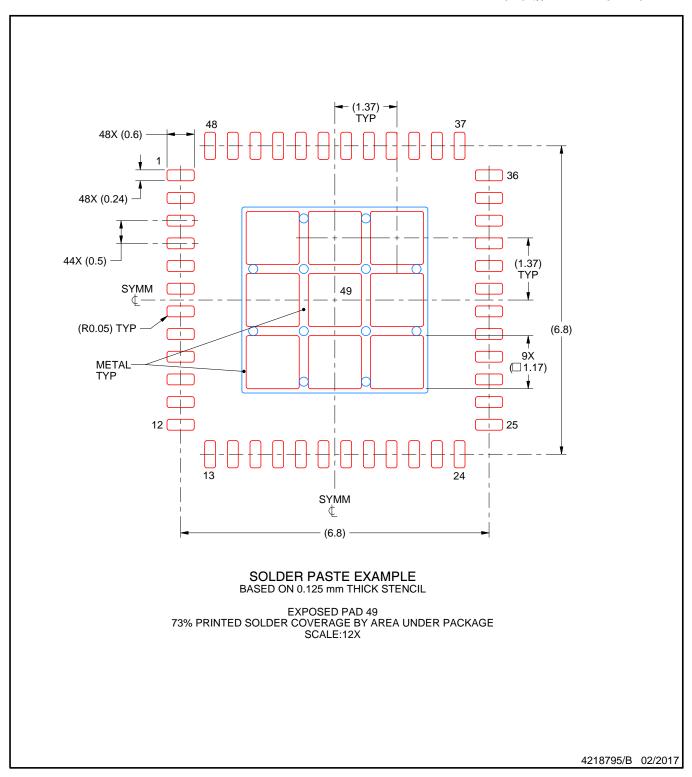

- 48-Pin 7-mm × 7-mm VQFN (RGZ) Package

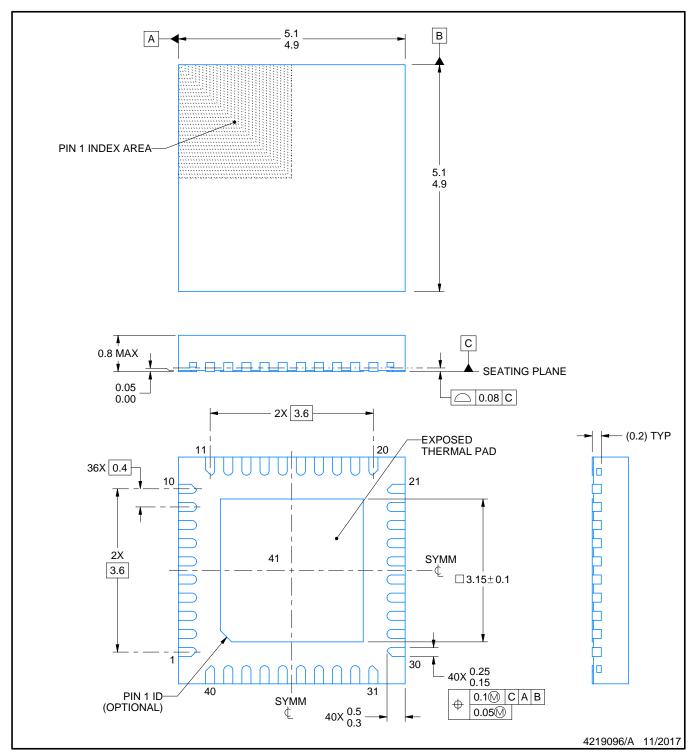

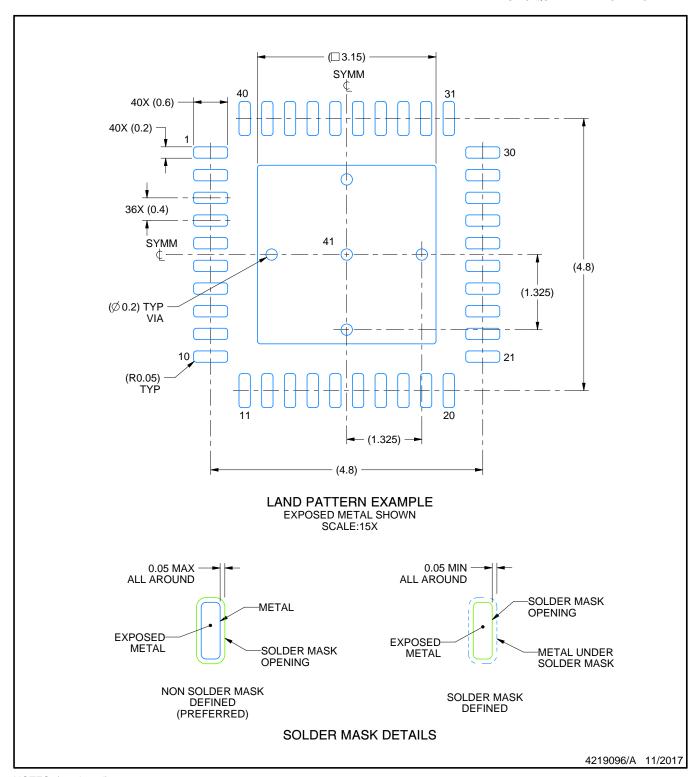

- 40-Pin 5-mm × 5-mm WQFN (RSB) Package

## 2 Applications

- Personal Computer Market

- DP/TMDS Dongle

- Desktop PC

- Notebook PC

- **Docking Station**

- Stand-Alone Video Card

## 3 Description

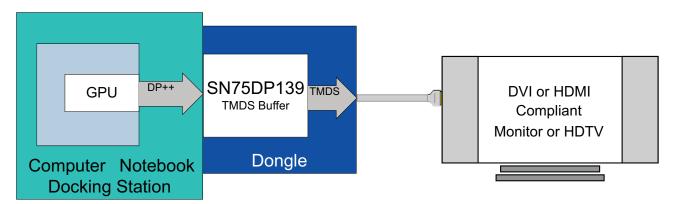

The SN75DP139 is a dual-mode DisplayPort input to Transition-Minimized Differential Signaling (TMDS) output. The TMDS output has a built-in level-shifting re-driver supporting Digital Video Interface (DVI) 1.0 and High Definition Multimedia Interface (HDMI) 1.4b standards. The SN75DP139 is specified up to a maximum data rate of 3.4 Gbps, supporting resolutions greater then 1920 x 1200 or HDTV 12-bit color depth at 1080p (progressive scan). The SN75DP139 is compliant with the HDMI 1.4b specifications and supports optional protocol enhancements such as 3D graphics at resolutions demanding a pixel rate up to 340 MHz.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| SN75DP139   | VQFN (48) | 7.00 mm x 7.00 mm |

|             | WQFN (40) | 5.00 mm x 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

#### **Typical Application**

GPU - Graphics Processing Unit

DP++ - Dual-Mode DisplayPort

TMDS - Transition-Minimized Differential Signaling

DVI - Digital Visual Interface

HDMI - High Definition Multimedia Interface

# **Table of Contents**

| 1      | Features 1                                                      |    | 7.1 Overview                                         | 18 |

|--------|-----------------------------------------------------------------|----|------------------------------------------------------|----|

| 2      | Applications 1                                                  |    | 7.2 Functional Block Diagram                         | 18 |

| 3      | Description 1                                                   |    | 7.3 Feature Description                              | 19 |

| 4      | Revision History2                                               |    | 7.4 Device Functional Modes                          | 22 |

| 5      | Pin Configuration and Functions4                                |    | 7.5 Programming                                      | 22 |

| 5<br>6 | Specifications7                                                 | 8  | Application and Implementation                       | 27 |

| U      | •                                                               |    | 8.1 Application Information                          | 27 |

|        | 6.1 Absolute Maximum Ratings                                    |    | 8.2 Typical Application                              | 27 |

|        | 6.3 Recommended Operating Conditions                            | 9  | Power Supply Recommendations                         | 29 |

|        | 6.4 Thermal Information                                         | 10 | Layout                                               | 29 |

|        | 6.5 Electrical Characteristics (Device Power)                   |    | 10.1 Layout Guidelines                               |    |

|        | 6.6 Electrical Characteristics (Hot Plug Detect)                |    | 10.2 Layout Example                                  |    |

|        | 6.7 Electrical Characteristics (Aux / I <sup>2</sup> C Pins)    | 11 | Device and Documentation Support                     |    |

|        | 6.8 Electrical Characteristics (TMDS and Main Link              |    | 11.1 Receiving Notification of Documentation Updates |    |

|        | Pins)                                                           |    | 11.2 Community Resources                             |    |

|        | 6.9 Switching Characteristics (Hot Plug Detect) 11              |    | 11.3 Trademarks                                      | 32 |

|        | 6.10 Switching Characteristics (Aux / I <sup>2</sup> C Pins) 12 |    | 11.4 Electrostatic Discharge Caution                 | 32 |

|        | 6.11 Switching Characteristics (TMDS and Main Link              |    | 11.5 Glossary                                        |    |

|        | Pins)14                                                         | 12 | Mechanical, Packaging, and Orderable                 |    |

|        | 6.12 Typical Characteristics                                    |    | Information                                          | 32 |

| 7      | Detailed Description 18                                         |    |                                                      |    |

|        |                                                                 |    |                                                      |    |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| CI | nanges from Revision E (September 2014) to Revision F                                                                                                                                                                                                                                                                            | Page |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added Note 1 to the Pin Functions table                                                                                                                                                                                                                                                                                          | 5    |

| •  | Changed the Handling Ratings To ESD Ratings and moved the Storage temperature range to the Absolute  Maximum Ratings                                                                                                                                                                                                             | 7    |

| CI | nanges from Revision D (July 2013) to Revision E                                                                                                                                                                                                                                                                                 | Page |

| •  | Added Pin Configuration and Functions section, Handling Rating table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1    |

| CI | nanges from Revision C (December 2012) to Revision D                                                                                                                                                                                                                                                                             | Page |

| •  | Changed title and Feature bullet from "TMDS Translator" to "TMDS Level Shifting Re-driver"                                                                                                                                                                                                                                       | 1    |

| •  | Changed second sentence text string in Description section from "built in level translator" to "built in level shifting re-driver"                                                                                                                                                                                               | 1    |

| C | hanges from Revision A (July 2010) to Revision B                   | Page |

|---|--------------------------------------------------------------------|------|

| • | Added to FEATURES "40 Pin 5 x 5 QFN (RSB) Package"                 | ·    |

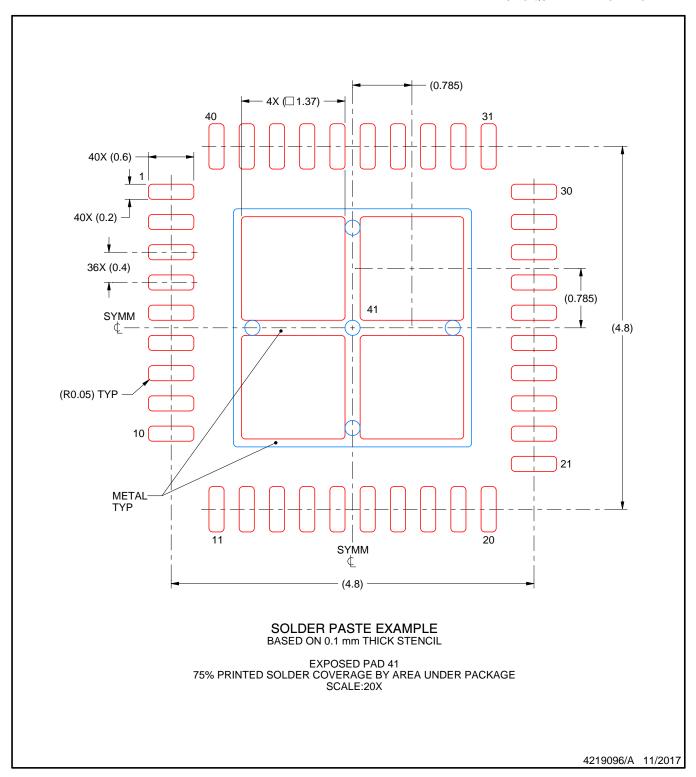

| • | Added RSB package drawing                                          | 4    |

| • | Changed Pin Functions to include RSB package pins                  | 8    |

| • | Added RSB package to ORDERING INFORMATION table                    | 6    |

| • | Changed voltage range section of Absolute Maximum Ratings          |      |

| • | Changed input voltages within the Recommended Operating Conditions |      |

| • | Changed thermal resistance info and enable voltages to 3.6V        | 8    |

| • | Changed enable voltages from 5 V to 3.6 V                          | 9    |

| • | Changed V <sub>IH(AUX</sub> ) max from 5.5 V to 3.6 V              | 9    |

| • | Changed OUT_Dx terminal connections                                | 18   |

|   |                                                                    |      |

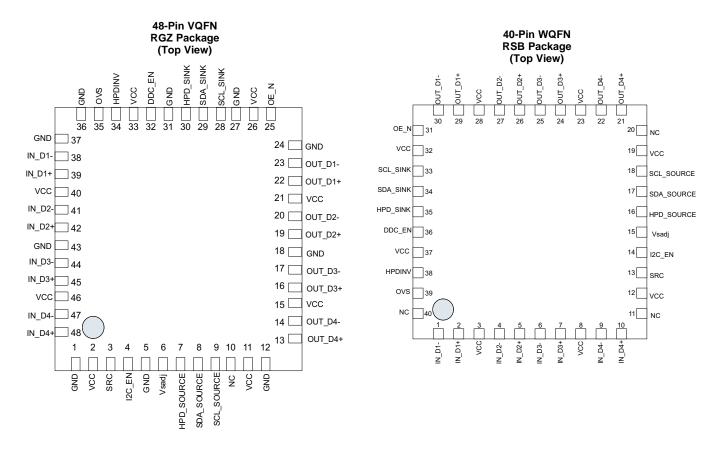

## 5 Pin Configuration and Functions

### **Pin Functions**

|                           | PIN                                                       |                                |     |                                                                                          |

|---------------------------|-----------------------------------------------------------|--------------------------------|-----|------------------------------------------------------------------------------------------|

| CIONAL                    | NO.                                                       |                                | I/O | DESCRIPTION                                                                              |

| SIGNAL                    | RGZ                                                       | RSB                            |     |                                                                                          |

| MAIN LINK INPU            | T PINS                                                    |                                |     |                                                                                          |

| IN_D1                     | 38, 39                                                    | 1, 2                           | I   | DisplayPort Main Link Channel 0 Differential Input                                       |

| IN_D2                     | 41, 42                                                    | 4, 5                           | I   | DisplayPort Main Link Channel 1 Differential Input                                       |

| IN_D3                     | 44, 45                                                    | 6, 7                           | I   | DisplayPort Main Link Channel 2 Differential Input                                       |

| IN_D4                     | 47, 48                                                    | 9, 10                          | ı   | DisplayPort Main Link Channel 3 Differential Input                                       |

| MAIN LINK POR             | T B OUTPUT PINS                                           |                                |     |                                                                                          |

| OUT_D1                    | 23, 22                                                    | 30, 29                         | 0   | TMDS Data 2 Differential Output                                                          |

| OUT_D2                    | 20, 19                                                    | 27, 26                         | 0   | TMDS Data 1 Differential Output                                                          |

| OUT_D3                    | 17, 16                                                    | 25, 24                         | 0   | TMDS Data 0 Differential Output                                                          |

| OUT_D4                    | 14, 13                                                    | 22, 21                         | 0   | TMDS Data Clock Differential Output                                                      |

| HOT PLUG DETI             | ECT PINS                                                  |                                |     |                                                                                          |

| HPD_SOURCE                | 7                                                         | 16                             | 0   | Hot Plug Detect Output                                                                   |

| HPD_SINK                  | 30                                                        | 35                             | I   | Hot Plug Detect Input                                                                    |

| <b>AUXILIARY DAT</b>      | A PINS                                                    |                                |     |                                                                                          |

| SDA_SOURCE,<br>SCL_SOURCE | 8, 9                                                      | 17, 18                         | I/O | Source Side Bidirectional DisplayPort Auxiliary Data Line                                |

| SDA_SINK,<br>SCL_SINK     | 29, 28                                                    | 34, 33                         | I/O | TMDS Port Bidirectional DDC Data Lines                                                   |

| CONTROL PINS              |                                                           |                                |     |                                                                                          |

| OE_N                      | 25                                                        | 31                             | ı   | Output Enable and power saving function for High Speed Differential level shifter path.  |

| NC                        | 10                                                        | 11, 20, 40                     |     | No Connect                                                                               |

| OVS                       | 35                                                        | 39                             | I   | DDC I2C buffer offset select                                                             |

| DDC_EN                    | 32                                                        | 36                             | I   | Enables or Disables the DDC I2C buffer                                                   |

| HPDINV                    | 34                                                        | 38                             | ı   | HPD_SOURCE Logic and Level Select                                                        |

| VSadj                     | 6                                                         | 15                             | I   | TMDS Compliant Voltage Swing Control                                                     |

| SRC                       | 3                                                         | 13                             | I   | TMDS outputs rise and fall time select                                                   |

| I2C_EN                    | 4                                                         | 14                             | I   | Internal I <sup>2</sup> C register enable, used for HDMI / DVI connector differentiation |

| SUPPLY AND G              | ROUND PINS                                                |                                |     |                                                                                          |

| VCC                       | 2, 11, 15, 21, 26,<br>33, 40, 46                          | 3, 8, 12, 19, 23<br>28, 32, 37 |     | 3.3 V Supply                                                                             |

| GND                       | 1, 5, 12, 18, 24,<br>27, 31, 36, 37,<br>43 <sup>(1)</sup> | Thermal Pad                    |     | Ground                                                                                   |

<sup>(1)</sup> Connect the Thermal Pad to GND

Product Folder Links: SN75DP139

# **Table 1. Control Pin Lookup Table**

| SIGNAL              | LEVEL <sup>(1)</sup> | STATE                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                |

|---------------------|----------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OE_N                | Н                    | Power Saving<br>Mode           | Main Link is disabled. IN_Dx termination = 50 $\Omega$ with common mode voltage set to 0V. OUT_Dx outputs = high impedance                                                                                                                                                                                                 |

|                     | L                    | Normal Mode                    | IN_Dx termination = $50 \Omega$<br>OUT_Dx outputs = active                                                                                                                                                                                                                                                                 |

| I <sup>2</sup> C_EN | Н                    | HDMI                           | The Internal I2C register is active and readable when the TMDS port is selected indicating that the connector being used is HDMI.  This mode selects the fastest rise and fall time for the TMDS differential output signals                                                                                               |

|                     | L                    | DVI                            | The Internal I2C register is disabled and not readable when the TMDS port is selected indicating that the connector being used is DVI.  This mode selects a slower rise and fall time for the TMDS differential output signals See <i>Application Information</i> .                                                        |

| VSadj               | 4.02 kΩ<br>±5%       | Output Voltage<br>Swing Contol | Driver output voltage swing precision control to aid with system compliance                                                                                                                                                                                                                                                |

| HPDINV              | Н                    | HPD Inversion                  | HPD_SOURCE VOH =0.9V (typical) and HPD logic is inverted                                                                                                                                                                                                                                                                   |

|                     | L                    | HPD non-<br>inversion          | HPD_SOURCE VOH =3.2V (typical) and HPD logic is non-inverted                                                                                                                                                                                                                                                               |

| SRC                 | Н                    | Edge Rate:<br>Slowest          | SRC helps to slow down the rise and fall time. SRC =High adds ~60ps to the rise and fall time of the TMDS differential output signals in addition to the I2C_EN pin selection (recommended setting)                                                                                                                        |

|                     | L                    | Edge Rate: Slow                | SRC helps to slow down the rise and fall time. SRC =Low adds ~30ps to the rise and fall time of the TMDS differential output signals in addition to the I <sup>2</sup> C_EN pin selection                                                                                                                                  |

|                     | Hi-Z                 | Edge Rate                      | Leaving the SRC pin High Z, will keep the default rise and fall time of the TMDS differential output signals as selected by the I $^2$ C_EN pin. It is recommended that an external resistor-divider (less than 100 k $\Omega$ ) is used so that voltage on this pin = VCC/2, if Hi-Z logic level is intended on this pin. |

| OVS                 | Н                    | Offset 1                       | DDC source side VOL and VIL offset range 1                                                                                                                                                                                                                                                                                 |

|                     | L                    | Offset 2                       | DDC source side VOL and VIL offset range 2                                                                                                                                                                                                                                                                                 |

|                     | Hi-Z                 | Offset 3                       | DDC source side VOL and VIL offset range 3 It is recommended that an external resistor-divider (less than 100 k $\Omega$ ) is used so that voltage on this pin = VCC/2, if Hi-Z logic level is intended on this pin.                                                                                                       |

| DDC_EN              | Н                    | DDC Buffer enabled             | DDC Buffer is enabled                                                                                                                                                                                                                                                                                                      |

|                     | L                    | DDC buffer disabled            | DDC Buffer is disabled                                                                                                                                                                                                                                                                                                     |

<sup>(1) (</sup>H) Logic High; (L) Logic Low; (Z) High Z

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                     |                                                                                  | MIN         | MAX       | UNIT |

|-------------------------------------|----------------------------------------------------------------------------------|-------------|-----------|------|

| Supply voltage range <sup>(2)</sup> | VCC                                                                              | -0.3        | 3.6       | V    |

|                                     | Main Link Input (IN_Dx) differential voltage                                     | -0.3        | VCC + 0.3 | V    |

| l                                   | TMDS Outputs (OUT_Dx)                                                            | -0.3        | VCC + 0.3 |      |

| Voltage range                       | HPD_SOURCE, SDA_SOURCE, SCL_SOURCE, OVS, DDC_EN, VSadj, SRC, I <sup>2</sup> C_EN | -0.3        | VCC + 0.3 |      |

|                                     | HPD_SINK, SDA_SINK, SCL_SINK, OE_EN, HPDINV                                      | -0.3        | 5.5       |      |

| Storage temperature ran             | ige, T <sub>stg</sub>                                                            | <b>-</b> 55 | 150       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                     | VALUE  | UNIT |

|--------------------|-------------------------|-------------------------------------|--------|------|

|                    |                         | Human body model <sup>(1)</sup>     | ±10000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model <sup>(2)</sup> | ±1500  | V    |

| (===)              |                         | Machine model <sup>(3)</sup>        | ±200   | V    |

<sup>(1)</sup> Tested in accordance with JEDEC Standard 22, Test Method A114-B

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                             |                                                        |                        | MIN  | NOM  | MAX | UNIT |

|-----------------------------|--------------------------------------------------------|------------------------|------|------|-----|------|

| V <sub>CC</sub>             | Supply Voltage                                         |                        | 3    | 3.3  | 3.6 | V    |

| T <sub>A</sub>              | Operating free-air temperature                         |                        | 0    |      | 85  | °C   |

| MAIN LINK DIFFERE           | ENTIAL INPUT PINS                                      |                        | •    |      |     |      |

| V <sub>ID_PP</sub>          | Peak-to-peak AC input differential voltage             |                        | 0.15 |      | 1.2 | V    |

| _                           | Dete sets                                              | RGZ package            | 0.25 |      | 3.4 | Char |

| d <sub>R</sub>              | Data rate                                              | RSB package            | 0.25 |      | 3.4 | Gbps |

| t <sub>rise fall time</sub> | Input Signal Rise and Fall time (20%-80%)              |                        | 75   |      |     | ps   |

| V <sub>PRE</sub>            | Pre-emphasis on the Input Signal at IN_Dx pins         |                        | 0    | 0    | 0   | db   |

| TMDS DIFFERENTIA            | AL OUTPUT PINS                                         |                        |      |      |     |      |

| AV <sub>CC</sub>            | TMDS output termination voltage                        |                        | 3    | 3.3  | 3.6 | V    |

| .1                          | Data and                                               | RGZ package            | 0.25 |      | 3.4 | 01   |

| d <sub>R</sub>              | Data rate                                              | RSB package            | 0.25 |      | 3.4 | Gbps |

| R <sub>T</sub>              | Termination resistance                                 |                        | 45   | 50   | 55  | Ω    |

| R <sub>Vsadj</sub>          | TMDS output swing voltage bias resistor <sup>(1)</sup> |                        | 3.65 | 4.02 |     | kΩ   |

| AUXILIARY AND 120           | PINS                                                   |                        | •    |      |     |      |

|                             | Landard                                                | SDA_SINK, SCL_SINK     | 0    |      | 5.5 |      |

| V <sub>I</sub>              | Input voltage                                          | SDA_SOURCE, SCL_SOURCE |      |      | 3.6 | V    |

| d <sub>R(I2C)</sub>         | I <sup>2</sup> C data rate                             | ,                      |      |      | 100 | kHz  |

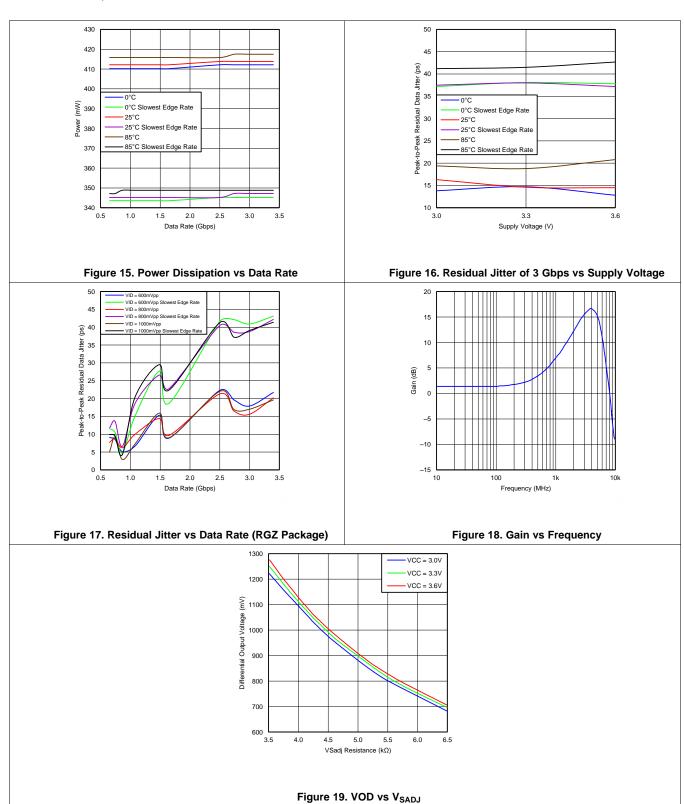

<sup>(1)</sup> R<sub>Vsadj</sub> resistor controls the SN75DP139 Driver output voltage swing and thus helps in meeting system compliance. It is recommended that R<sub>Vsadj</sub> resistor should be above the MIN value as indicated in the RECOMMENDED OPERATING CONDITIONS table, however for NOM and MAX value, Figure 19 could be used as reference. It is important to note that system level losses, AV<sub>CC</sub> and R<sub>T</sub> variation affect R<sub>Vsadj</sub> resistor selection. Worse case variation on system level losses, AV<sub>CC</sub>, R<sub>T</sub> could make R<sub>Vsadj</sub> resistor value of 4.02 kΩ ±5% result in non-compliant TMDS output voltage swing. In such cases Figure 19 could be used as reference.

<sup>(2)</sup> All voltage values, except differential voltages, are with respect to network ground terminal.

<sup>2)</sup> Tested in accordance with JEDEC Standard 22, Test Method C101-A

<sup>(3)</sup> Tested in accordance with JEDEC Standard 22, Test Method A115-A

## **Recommended Operating Conditions (continued)**

over operating free-air temperature range (unless otherwise noted)

|                         |                          | MIN | NOM | MAX | UNIT |

|-------------------------|--------------------------|-----|-----|-----|------|

| HPD_SINK, HPDIN         | /, OE_N                  |     |     |     |      |

| V <sub>IH</sub>         | High-level input voltage | 2   |     | 5.5 | V    |

| V <sub>IL</sub>         | Low-level input voltage  | 0   |     | 8.0 | V    |

| DDC_EN, I2C_EN          |                          | •   |     |     |      |

| V <sub>IH</sub>         | High-level input voltage | 2   |     | 3.6 | V    |

| $V_{IL}$                | Low-level input voltage  | 0   |     | 8.0 | V    |

| SRC, OVS                |                          | •   |     |     |      |

| V <sub>IH_SRC_OVS</sub> | High-level input voltage | 3   |     | 3.6 | V    |

| V <sub>IL_SRC_OVS</sub> | Low-level input voltage  | 0   |     | 0.5 | V    |

#### 6.4 Thermal Information

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                                                          | TEST CONDITION                                                                                                                                        | NS          | MIN TYP | MAX <sup>(1)</sup> | UNIT  |

|-------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|--------------------|-------|

| 0                 | Junction-to-board thermal                                                          |                                                                                                                                                       | RGZ package | 10.9    |                    | °C/W  |

| $\theta_{\sf JB}$ | resistance                                                                         |                                                                                                                                                       | RSB package | 10.8    |                    | °C/VV |

| 0                 | Junction-to-case-top thermal                                                       |                                                                                                                                                       | RGZ package | 22.5    |                    | °C/W  |

| $\theta_{JCT}$    | resistance                                                                         |                                                                                                                                                       | RSB package | 24.4    |                    | 0/8   |

| 111               | Junction-to-board thermal                                                          | High-K board (2)                                                                                                                                      | RGZ package | 10.9    |                    | °C/W  |

| ΨЈВ               | resistance metric                                                                  | Tigh-R board                                                                                                                                          | RSB package | 10.8    |                    | C/VV  |

| W                 | Junction-to-top thermal resistance                                                 | High-K board <sup>(2)</sup>                                                                                                                           | RGZ package | 0.5     |                    | °C/W  |

| ΨJT               | metric                                                                             | Tilgii-N board                                                                                                                                        | RSB package | 0.4     |                    | 0,    |

| P <sub>D1</sub>   | Device power dissipation <sup>(3)</sup>                                            | HDMI Mode: OE_N = 0V, DDC_EN = 3.6' ML: VID_PP = 1200mV, 3Gbps TMDS pat AUX: V <sub>1</sub> = 3.3V, 100 kHz PRBS HPD: HPD_SINK = 5V, I2C_EN = 3.6V, S | ttern       | 270+146 | 396+146            | mW    |

| P <sub>D2</sub>   | Device power dissipation <sup>(3)</sup>                                            | DVI Mode: OE_N = 0V, DDC_EN = 3.6V, ML: VID_PP = 1200mV, 3Gbps TMDS par AUX: V <sub>I</sub> = 3.3V, 100 kHz PRBS HPD: HPD_SINK= 5V, I2C_EN = 0V, SR0  | ttern       | 214+146 | 306+146            | mW    |

| P <sub>SD1</sub>  | Device power dissipation under low power with<br>HPDINV = LOW                      | OE_N = 5V, DDC_EN = 0V, HPDINV = 0\<br>HPD_SINK = 0V                                                                                                  | J,          | 18      | 54                 | μW    |

| P <sub>SD2</sub>  | Device power dissipation under low power with<br>HPDINV =HIGH                      | OE_N = 5V, DDC_EN = 0V, HPDINV = 5\                                                                                                                   | /           | 1.7     | 3                  | mW    |

| P <sub>SD3</sub>  | Device power dissipation under low<br>power with DDC enabled with<br>HPDINV = HIGH | OE_N = 5V, DDC_EN = 3.6V, HPDINV =                                                                                                                    | 5V          | 16.5    | 29                 | mW    |

| P <sub>SD4</sub>  | Device power dissipation under low power with DDC enabled with HPDINV = LOW        | OE_N = 5V, DDC_EN = 3.6V, HPDINV =                                                                                                                    | 0V          | 15      | 26                 | mW    |

Submit Documentation Feedback

Copyright © 2009–2017, Texas Instruments Incorporated

The maximum rating is simulated under 3.6V V<sub>CC</sub> unless otherwise noted.

Test conditions for ψ<sub>JB</sub> and ψ<sub>JT</sub> are clarified in TI document *Semiconductpr and IC Package Thermal Metrics*, .

Power dissipation is the sum of the power consumption from the VCC pins, plus the 146 mW of power from the AVCC (HDMI/DVI Receiver Termination Supply).

## 6.5 Electrical Characteristics (Device Power)

over operating free-air temperature range (unless otherwise noted)

|                  | PARAMETER                                            | TEST CONDITIONS                                                                                                                                                                                                                                                  | MIN | TYP | MAX | UNIT |

|------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>CC1</sub> | Supply current (HDMI Mode)                           | HDMI Mode: OE_N = 0V, DDC_EN = $3.6 \text{ V}$ , $V_{CC}$ = $3.6 \text{ V}$ , ML: VID_PP = $1200 \text{ mV}$ , 3 Gbps TMDS pattern AUX: $V_I$ = $3.3 \text{ V}$ , $100 \text{ kHz}$ PRBS HPD: HPD_SINK = $5 \text{ V}$ , $12C_EN$ = $3.6 \text{ V}$ , SRC = Hi-Z |     | 82  | 110 | mA   |

| I <sub>CC2</sub> | Supply Current (DVI Mode)                            | DVI Mode: OE_N = 0V, DDC_EN = 3.6 V, V <sub>CC</sub> = 3.6 V, ML: VID_PP = 1200 mV, 3 Gbps TMDS pattern AUX: V <sub>I</sub> = 3.3 V, 100 kHz PRBS HPD: HPD_SINK= 5 V, I2C_EN = 0 V, SRC = Hi-Z                                                                   |     | 65  | 85  | mA   |

| I <sub>SD1</sub> | Shutdown current with HPDINV = LOW                   | OE_N = 5 V, DDC_EN = 0 V, HPDINV = 0 V,<br>HPD_SINK = 0 V                                                                                                                                                                                                        |     | 5.5 | 15  | μΑ   |

| I <sub>SD2</sub> | Shutdown current with HPDINV = HIGH                  | OE_N = 5 V, DDC_EN = 0 V, HPDINV = 5 V                                                                                                                                                                                                                           |     | 0.5 | 0.8 | mA   |

| I <sub>SD3</sub> | Shutdown current with DDC enabled with HPDINV = HIGH | OE_N = 5 V, DDC_EN = 3.6 V, HPDINV = 5 V                                                                                                                                                                                                                         |     | 5   | 8   | mA   |

| I <sub>SD4</sub> | Shutdown current with DDC enabled with HPDINV = LOW  | OE_N = 5 V, DDC_EN = 3.6 V, HPDINV = 0 V                                                                                                                                                                                                                         |     | 4.5 | 7.2 | mA   |

## 6.6 Electrical Characteristics (Hot Plug Detect)

over recommended operating conditions (unless otherwise noted)

|                     | interface operating containers (amose othe |                                                               |     |     |     |      |

|---------------------|--------------------------------------------|---------------------------------------------------------------|-----|-----|-----|------|

|                     | PARAMETER                                  | TEST CONDITIONS                                               | MIN | TYP | MAX | UNIT |

| V <sub>OH3.3</sub>  | High-level output voltage                  | $I_{OH}$ = -100 $\mu$ A, $V_{CC}$ = 3.3 V ±10%, HPDINV = LOW  | 2.8 |     | 3.6 | V    |

| V <sub>OH1.1</sub>  | High-level output voltage                  | $I_{OH}$ = -100 $\mu$ A, $V_{CC}$ = 3.3 V ±10%, HPDINV = HIGH | 0.8 |     | 1.1 | V    |

| V <sub>OL</sub>     | Low-level output voltage                   | I <sub>OH</sub> = 100 μA                                      | 0   |     | 0.1 | V    |

| I <sub>IH</sub>     | High-level input current                   | $V_{IH} = 2.0 \text{ V}, V_{CC} = 3.6 \text{ V}$              | -30 |     | 30  | μΑ   |

| I <sub>IL</sub>     | Low-level input current                    | $V_{IL} = 0.8 \text{ V}, V_{CC} = 3.6 \text{ V}$              | -30 |     | 30  | μΑ   |

| R <sub>INTHPD</sub> | Input pull down on HPD_SINK (HPD Input)    |                                                               | 110 | 130 | 160 | kΩ   |

# 6.7 Electrical Characteristics (Aux / I<sup>2</sup>C Pins)

over recommended operating conditions (unless otherwise noted)

|                             | PARAMETER                |                                                          | TEST CONDITIONS                                | MIN  | TYP MAX | UNIT |

|-----------------------------|--------------------------|----------------------------------------------------------|------------------------------------------------|------|---------|------|

| IL                          | Low input current        |                                                          | V <sub>CC</sub> = 3.6 V, V <sub>I</sub> = 0 V  | -10  | 10      | μΑ   |

| I <sub>lkg(AUX)</sub>       | Input leakage current    | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | V <sub>CC</sub> = 3.6V, V <sub>I</sub> = 3.6 V | -10  | 10      | μΑ   |

| C <sub>IO(AUX)</sub>        | Input/Output capacitance | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | DC bias = 1.65 V, AC = 2.1Vp-p,<br>f = 100 kHz |      | 15      | pF   |

| $V_{\text{IH}(\text{AUX})}$ | High-level input voltage | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) |                                                | 1.6  | 3.6     | V    |

| V <sub>IL1(AUX)</sub>       | Low-level input voltage  | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | OVS = HIGH                                     | -0.2 | 0.36    | V    |

| V <sub>OL1(AUX)</sub>       | Low-level output voltage | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | I <sub>O</sub> = 3 mA, OVS = HIGH              | 0.6  | 0.7     | V    |

Product Folder Links: SN75DP139

# Electrical Characteristics (Aux / I<sup>2</sup>C Pins) (continued)

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                |                                                          | TEST CONDITIONS                                  | MIN        | TYP MAX | UNIT |

|-----------------------|--------------------------|----------------------------------------------------------|--------------------------------------------------|------------|---------|------|

| V <sub>IL2(AUX)</sub> | Low-level input voltage  | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | OVS = Hi-Z                                       | -0.2       | 0.36    | V    |

| V <sub>OL2(AUX)</sub> | Low-level output voltage | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | I <sub>O</sub> = 3 mA, OVS = Hi-Z                | 0.5        | 0.6     | V    |

| V <sub>IL3(AUX)</sub> | Low-level input voltage  | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | OVS = Low                                        | -0.2       | 0.27    | V    |

| V <sub>OL3(AUX)</sub> | Low-level output voltage | AUX_I <sup>2</sup> C pins<br>(SCL_SOURCE,<br>SDA_SOURCE) | I <sub>O</sub> = 3 mA, OVS = Low                 | 0.4        | 0.5     | V    |

| I <sub>lkg(I2C)</sub> | Input leakage current    | I <sup>2</sup> C SDA/SCL pins<br>(SCL_SINK,<br>SDA_SINK) | V <sub>CC</sub> = 3.6 V, V <sub>I</sub> = 4.95 V | <b>–10</b> | 10      | μА   |

| C <sub>IO(I2C)</sub>  | Input/Output capacitance | I <sup>2</sup> C SDA/SCL pins<br>(SCL_SINK,<br>SDA_SINK) | DC bias = 2.5 V, AC = 3.5Vp-p, f<br>= 100 kHz    |            | 15      | pF   |

| V <sub>IH(I2C)</sub>  | High-level input voltage | I <sup>2</sup> C SDA/SCL pins<br>(SCL_SINK,<br>SDA_SINK) |                                                  | 2.1        | 5.5     | V    |

| V <sub>IL(I2C)</sub>  | Low-level input voltage  | I <sup>2</sup> C SDA/SCL pins<br>(SCL_SINK,<br>SDA_SINK) |                                                  | -0.2       | 1.5     | V    |

| V <sub>OL(I2C)</sub>  | Low-level output voltage | I <sup>2</sup> C SDA/SCL pins<br>(SCL_SINK,<br>SDA_SINK) | I <sub>O</sub> = 3mA                             |            | 0.2     | V    |

# 6.8 Electrical Characteristics (TMDS and Main Link Pins)

over recommended operating conditions (unless otherwise noted)

|                     | PARAMETER                                                              | TEST CONDITIONS                                                           | MIN      | TYP | MAX      | UNIT |

|---------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------|----------|-----|----------|------|

| V <sub>OH</sub>     | Single-ended HIGH level output voltage                                 | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ ,                                       | AVCC-10  |     | AVCC+10  | mV   |

| V <sub>OL</sub>     | Single-ended LOW level output voltage                                  |                                                                           | AVCC-600 |     | AVCC-400 | mV   |

| V <sub>SWING</sub>  | Single-ended output voltage swing                                      |                                                                           | 400      |     | 600      | mV   |

| V <sub>OC(SS)</sub> | Change in steady-state common-mode output voltage between logic states |                                                                           | -5       |     | 5        | mV   |

| V <sub>OD(PP)</sub> | Peak-to-Peak output differential voltage                               |                                                                           | 800      |     | 1200     | mV   |

| $V_{(O)SBY}$        | Single-ended standby output voltage                                    | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ , OE_N = High                           | AVCC-10  |     | AVCC+10  | mV   |

| I <sub>(O)OFF</sub> | Single-ended power down output current                                 | $0V \le VCC \le 1.5 \text{ V, AVCC} = 3.3 \text{ V,}$<br>$R_T = 50\Omega$ | -10      |     | 10       | μΑ   |

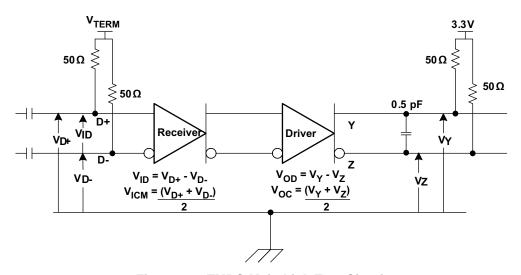

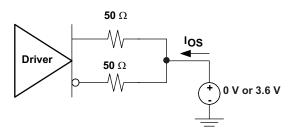

| Ios                 | Short circuit output current                                           | See Figure 14                                                             | -15      |     | 15       | mA   |

| R <sub>INT</sub>    | Input termination impedance                                            |                                                                           | 40       | 50  | 60       | Ω    |

| V <sub>term</sub>   | Input termination voltage                                              |                                                                           | 1        |     | 2        | V    |

Submit Documentation Feedback

Copyright © 2009–2017, Texas Instruments Incorporated

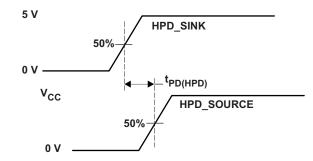

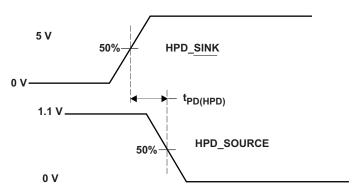

## 6.9 Switching Characteristics (Hot Plug Detect)

over recommended operating conditions (unless otherwise noted)

|                      | PARAMETER         | TEST CONDITIONS         | MIN | TYP MAX | UNIT |

|----------------------|-------------------|-------------------------|-----|---------|------|

| t <sub>PD(HPD)</sub> | Propagation delay | V <sub>CC</sub> = 3.6 V | 2   | 30      | ns   |

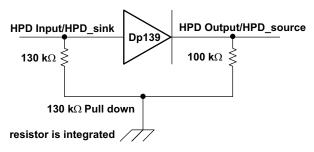

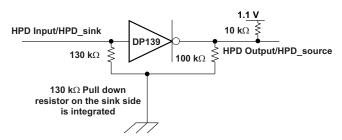

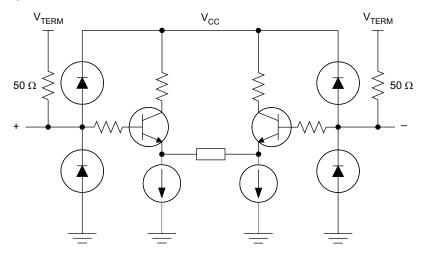

Figure 1. HPD Test Circuit (HPDINV = LOW)

Figure 2. HPD Test Circuit (VOH = 1.1), HPDINV = HIGH

Figure 3. HPD Timing Diagram (HPDINV = LOW)

Figure 4. HPD Timing Diagram (HPDINV = HIGH)

Copyright © 2009–2017, Texas Instruments Incorporated

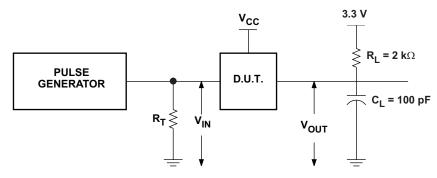

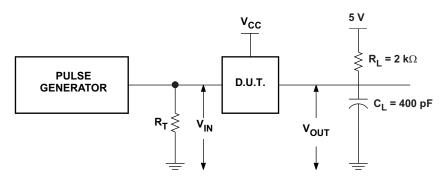

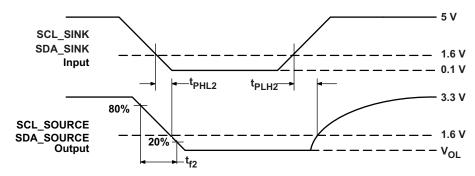

## 6.10 Switching Characteristics (Aux / I<sup>2</sup>C Pins)

over recommended operating conditions (unless otherwise noted)

|                    | PARAMETER                                              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------------------|-----------------|-----|-----|-----|------|

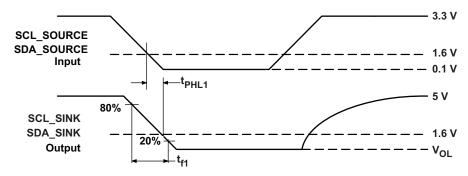

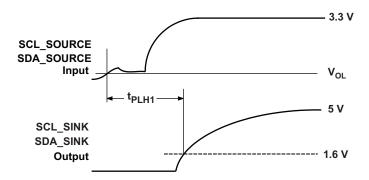

| t <sub>PLH1</sub>  | Propagation delay time, low to high                    | Source to Sink  | 204 |     | 600 | ns   |

| t <sub>PHL1</sub>  | Propagation delay time, high to low                    | Source to Sink  | 35  |     | 200 | ns   |

| t <sub>PLH2</sub>  | Propagation delay time, low to high                    | Sink to Source  | 80  |     | 251 | ns   |

| t <sub>PHL2</sub>  | Propagation delay time, high to low                    | Sink to Source  | 35  |     | 200 | ns   |

| t <sub>f1</sub>    | Output signal fall time                                | Sink Side       | 20  |     | 72  | ns   |

| t <sub>f2</sub>    | Output signal fall time                                | Source Side     | 20  |     | 72  | ns   |

| f <sub>SCL</sub>   | SCL clock frequency for internal register              | Source Side     |     |     | 100 | kHz  |

| t <sub>W(L)</sub>  | Clock LOW period for I <sup>2</sup> C register         | Source Side     | 4.7 |     |     | μS   |

| t <sub>W(H)</sub>  | Clock HIGH period for internal register                | Source Side     | 4.0 |     |     | μS   |

| t <sub>SU1</sub>   | Internal register setup time, SDA to SCL               | Source Side     | 250 |     |     | ns   |

| t <sub>h(1)</sub>  | Internal register hold time, SCL to SDA                | Source Side     | 0   |     |     | μS   |

| T <sub>(buf)</sub> | Internal register bus free time between STOP and START | Source Side     | 4.7 |     |     | μS   |

| t <sub>su(2)</sub> | Internal register setup time, SCL to START             | Source Side     | 4.7 |     |     | μS   |

| t <sub>h(2)</sub>  | Internal register hold time, START to SCL              | Source Side     | 4.0 |     |     | μS   |

| t <sub>su(3)</sub> | Internal register hold time, SCL to STOP               | Source Side     | 4.0 |     |     | μS   |

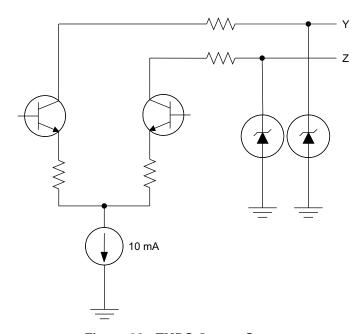

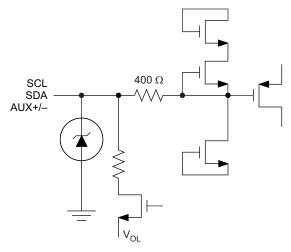

Figure 5. Source Side Test Circuit (SCL\_SOURCE, SDA\_SOURCE)

Figure 6. Sink Side Test Circuit (SCL\_SINK,SDA\_SINK)

Figure 7. Source Side Output AC Measurements

Figure 8. Sink Side Output AC Measurements

Figure 9. Sink Side Output AC Measurements Continued

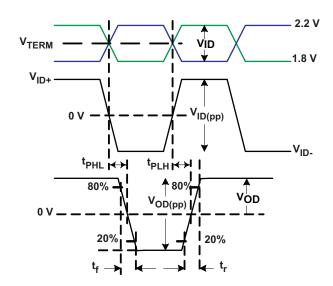

# 6.11 Switching Characteristics (TMDS and Main Link Pins)

over recommended operating conditions (unless otherwise noted)

|                       | PARAMETER                                 | TEST CONDITIONS                                                                                                                           | MIN | TYP | MAX | UNIT |

|-----------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>PLH</sub>      | Propagation delay time                    |                                                                                                                                           | 250 | 350 | 600 | ps   |

| t <sub>PHL</sub>      | Propagation delay time                    |                                                                                                                                           | 250 | 350 | 600 | ps   |

| t <sub>R1</sub>       | Rise Time (I2C_EN = HI, SRC = Hi-Z)       |                                                                                                                                           | 60  | 85  | 120 | ps   |

| t <sub>F1</sub>       | Fall Time (I2C_EN = HI, SRC = Hi-Z)       |                                                                                                                                           | 60  | 85  | 120 | ps   |

| t <sub>R2</sub>       | Rise Time (I2C_EN = Low, SRC = Hi-Z)      |                                                                                                                                           |     | 115 | 150 | ps   |

| t <sub>F2</sub>       | Fall Time (I2C_EN = Low, SRC = Hi-Z)      |                                                                                                                                           |     | 115 | 150 | ps   |

| t <sub>R3</sub>       | Rise Time (I2C_EN = HI, SRC = HI)         |                                                                                                                                           |     | 150 | 180 | ps   |

| t <sub>F3</sub>       | Fall Time (I2C_EN = HI, SRC = HI)         |                                                                                                                                           |     | 150 | 180 | ps   |

| t <sub>R4</sub>       | Rise Time (I2C_EN = HI, SRC = Low)        | AVCC=3.3 V, $R_T$ = 50 $\Omega$ , f = 1MHz,<br>$R_{Vsadj}$ = 4.02 k $\Omega$                                                              |     | 115 | 150 | ps   |

| t <sub>F4</sub>       | Fall Time (I2C_EN = HI, SRC = Low)        | TVsadj = 4.02 Ki2                                                                                                                         |     | 115 | 150 | ps   |

| t <sub>R5</sub>       | Rise Time (I2C_EN = Low, SRC = HI)        |                                                                                                                                           |     | 175 | 220 | ps   |

| t <sub>F5</sub>       | Fall Time (I2C_EN = Low, SRC = HI)        |                                                                                                                                           |     | 175 | 220 | ps   |

| t <sub>R6</sub>       | Rise Time (I2C_EN = Low, SRC = Low)       |                                                                                                                                           |     | 150 | 180 | ps   |

| t <sub>F6</sub>       | Fall Time (I2C_EN = Low, SRC = Low)       |                                                                                                                                           |     | 150 | 180 | ps   |

| t <sub>SK(P)</sub>    | Pulse skew                                |                                                                                                                                           |     | 8   | 15  | ps   |

| t <sub>SK(D)</sub>    | Intra-pair skew                           |                                                                                                                                           |     | 20  | 65  | ps   |

| t <sub>SK(O)</sub>    | Inter-pair skew                           |                                                                                                                                           |     | 20  | 100 | ps   |

| t <sub>JITD(PP)</sub> | Peak-to-peak output residual data jitter  | AVCC = 3.3 V, $R_T$ = 50 $\Omega$ , dR = 3Gbps,<br>TMDS output slew rate (default).<br>$R_{Vsadj}$ = 4.02 k $\Omega$ (refer to Figure 13) |     | 14  | 50  | ps   |

| t <sub>JITC(PP)</sub> | Peak-to-peak output residual clock jitter | AVCC = 3.3 V, $R_T = 50\Omega$ , $f = 300$ MHz<br>TMDS output slew rate (default).<br>$R_{Vsadj} = 4.02$ k $\Omega$ (refer to Figure 13)  |     | 8   | 30  | ps   |

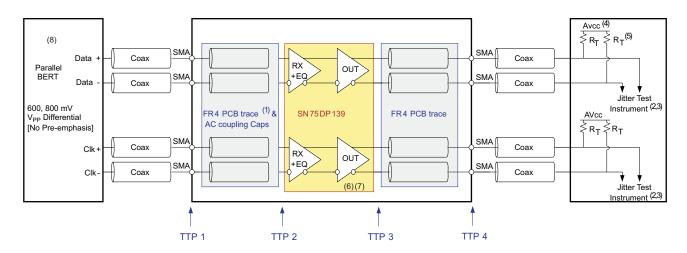

Figure 10. TMDS Main Link Test Circuit

Figure 11. TMDS Main Link Timing Measurements

Figure 12. TMDS Main Link Common Mode Measurements

- 1. The FR4 trace between TTP1 and TTP2 is designed to emulate 1-8" of FR4, AC coupling cap, connector and another 1-8" of FR4. Trace width 4 mils.

- All Jitter is measured at a BER of 10°

Residual jitter reflects the total jitter measured at TTP4 minus the jitter measured at TTP1

- 4. AVCC = 3.3V 5. RT = 50Ω,

- 6. Jitter data is taken with SN75DP139 configured in the fastest slew rate setting(default) 7. Rvsadj =  $4.02k\Omega$

- 8. The input signal from parallel BERT does not have any pre-emphasis. Refer to recommended operating conditions

Figure 13. TMDS Jitter Measurements

Figure 14. TMDS Main Link Short Circuit Output Circuit

## 6.12 Typical Characteristics

AVCC = 3.3 V,  $R_T = 50 \Omega$

## 7 Detailed Description

#### 7.1 Overview

The SN75DP139 is a Dual-Mode DisplayPort input to Transition-Minimized Differential Signaling (TMDS) output. The TMDS output has a built in level shifting re-driver supporting Digital Video Interface (DVI) 1.0 and High Definition Multimedia Interface (HDMI) 1.4b standards.

An integrated Active I2C buffer isolates the capacitive loading of the source system from that of the sink and interconnecting cable. This isolation improves overall signal integrity of the system and allows for considerable design margin within the source system for DVI / HDMI compliance testing.

A logic block was designed into the SN75DP139 in order to assist with TMDS connector identification. Through the use of the I2C\_EN pin, this logic block can be enabled to indicate the translated port is an HDMI port; therefore legally supporting HDMI content.

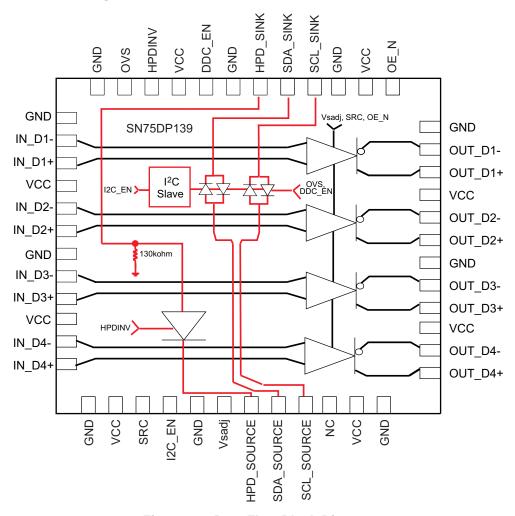

#### 7.2 Functional Block Diagram

Figure 20. Data Flow Block Diagram

#### 7.3 Feature Description

The SN75DP139 is designed to operate off of one supply voltage VCC.

The SN75DP139 offers features to enable or disable different functionality based on the status of the output enable (OE\_N) and DDC Enable (DDC\_EN) inputs.

- OE\_N affects only the High Speed Differential channels (Main Link/TMDS link). OE\_N has no influence on the HPD\_SINK input, HPD\_SOURCE output, or the DDC buffer.

- DDC\_EN affects only the DDC channel. The DDC\_EN should never change state during the I2C operation.

Disabling DDC\_EN during a bus operation will hang the bus, while enabling the DDC\_EN during bus traffic will corrupt the I2C bus operation. DDC\_EN should only be toggled while the bus is idle.

- TMDS output edge rate control has impact on the SN75DP139 Active power. See Figure 15. TMDS output

edge rate can be controlled by SRC pin. Slower output Edge Rate Setting helps in reducing the Active power

consumption.

| HPD_SINK       | HPDINV | OE_N | DDC_EN | IN_Dx                                                                        | OUT_Dx             | DDC                | HPD_SOURCE                              | MODE                                     |

|----------------|--------|------|--------|------------------------------------------------------------------------------|--------------------|--------------------|-----------------------------------------|------------------------------------------|

| Input = H or L | L      | L    | L      | 50 Ω termination active                                                      | Enabled            | High-<br>impedance | Output = non inverted, follows HPD_SINK | Active                                   |

| Input = H or L | L      | L    | Н      | 50 Ω termination active                                                      | Enabled            | enabled            | Output = non inverted, follows HPD_SINK | Active                                   |

| Input = H or L | L      | Н    | L      | 50 Ω termination active: Terminations connected to common Mode Voltage = 0V. | High-<br>impedance | High-<br>impedance | Output = non inverted, follows HPD_SINK | Low Power                                |

| Input = H or L | L      | Н    | Н      | 50 Ω termination active: Terminations connected to common Mode Voltage = 0V. | High-<br>impedance | enabled            | Output = non inverted, follows HPD_SINK | Low Power with<br>DDC channel<br>enabled |

| Input = H or L | Н      | L    | L      | 50 Ω termination active                                                      | Enabled            | High-<br>impedance | Output = inverted, follows<br>HPD_SINK  | Active                                   |

| Input = H or L | Н      | L    | Н      | 50 Ω termination active                                                      | Enabled            | enabled            | Output = inverted, follows<br>HPD_SINK  | Active                                   |

| Input = H or L | Н      | Н    | L      | 50 Ω termination active: Terminations connected to common Mode Voltage = 0V. | High-<br>impedance | High-<br>impedance | Output = inverted, follows<br>HPD_SINK  | Low Power                                |

| Input = H or L | Н      | Н    | Н      | 50 Ω termination active: Terminations connected to common Mode Voltage = 0V. | High-<br>impedance | enabled            | Output = inverted, follows<br>HPD_SINK  | Low Power with<br>DDC channel<br>enabled |

**Table 2. Packaging Options**

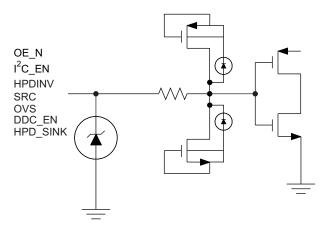

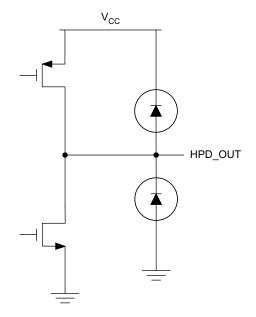

### 7.3.1 Hot Plug Detect

The SN75DP139 has a built in level shifter for the HPD outputs. The output voltage level of the HPD pin is defined by the voltage level of the VCC pin. The HPD input or HPD\_SINK side has 130kohm of pull down resistor integrated.

The logic of the HPD\_SOURCE output always follows the logic state of the HPD\_SINK input based on the HPDINV pin logic, regardless of whether the device is in Active or Low Power Mode

#### 7.3.2 Aux / I<sup>2</sup>C Pins

The SN75DP139 utilizes an active  $I^2C$  repeater. The repeater is designed to isolate the parasitic effects of the system in order to aid with system level compliance.

In addition to the I<sup>2</sup>C repeater, the SN75DP139 also supports the connector detection I<sup>2</sup>C register. This register is enabled via the I<sup>2</sup>C\_EN pin. When active an internal memory register is readable via the AUX\_I<sup>2</sup>C I/O. The functionality of this register block is described in the *Programming* section.

Product Folder Links: SN75DP139

#### 7.3.3 TMDS and Main Link Pins

The main link inputs are designed to support DisplayPort 1.1 specification. The TMDS outputs of the SN75DP139 are designed to support the Digital Video Interface (DVI) 1.0 and High Definition Multimedia Interface (HDMI) 1.4b specifications. The differential output voltage swing can be fine tuned with the  $R_{Vsadj}$  resistor.

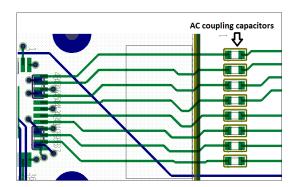

The DP++ (dual-mode) input of the SN75DP139 is designed to accommodate the standard DP level ac coupled signal with no pre-emphasis with up to 16 inches of trace (4 mil 100  $\Omega$  differential stripline).

### 7.3.4 Input/Output Equivalent Circuits

Figure 21. DisplayPort Input Stage

Figure 22. TMDS Output Stage

Figure 23. HPD and Control Input Stage

Figure 24. HPD Output Stage

Figure 25. I<sup>2</sup>C Input and Output Stage

#### 7.4 Device Functional Modes

#### **7.4.1** Active

The SN75DP139 activates the main link channel and thus is able to transmit the TMDS content.

#### 7.4.2 Low Power With DDC Channel Enabled

The SN75DP139 is in low power but keeps its DDC channel active, this allows the device to configure its internal I2C registers.

#### 7.4.3 Low Power

The SN75DP139 is in the lowest power mode, with no activity on the DDC or main link channels.

## 7.5 Programming

#### 7.5.1 I<sup>2</sup>C Interface Notes

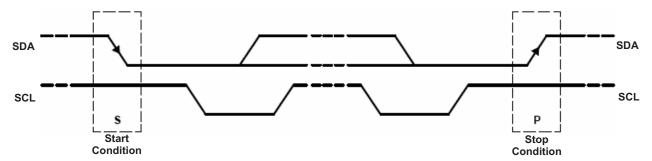

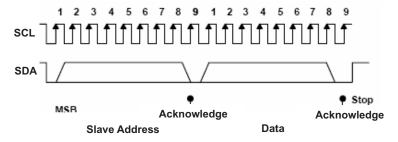

The I<sup>2</sup>C interface can be used to access the internal memory of the SN75DP139. I<sup>2</sup>C is a two-wire serial interface developed by Philips Semiconductor (see I<sup>2</sup>C-Bus Specification, Version 2.1, January 2000). The bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures. When the bus is *idle*, both SDA and SCL lines are pulled high. All the I<sup>2</sup>C compatible devices connect to the I<sup>2</sup>C bus through open drain I/O pins, SDA and SCL. A *master* device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. A *slave* device receives and/or transmits data on the bus under control of the master device. The SN75DP139 works as a slave and supports the standard mode transfer (100 kbps) as defined in the I<sup>2</sup>C-Bus Specification.

The basic I<sup>2</sup>C start and stop access cycles are shown in Figure 26.

The basic access cycle consists of the following:

- · A start condition

- A slave address cycle

- Any number of data cycles

- A stop condition

Figure 26. I<sup>2</sup>C Start And Stop Conditions

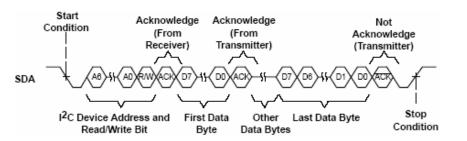

#### 7.5.2 General I<sup>2</sup>C Protocol

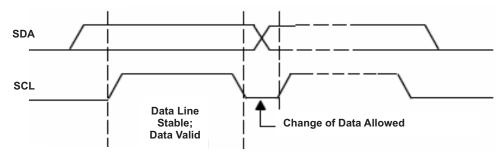

- The master initiates data transfer by generating a start condition. The start condition is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in Figure 28. All I<sup>2</sup>C-compatible devices should recognize a start condition.

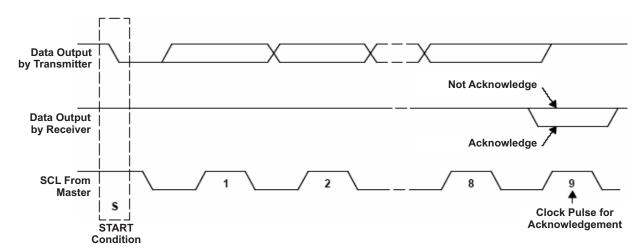

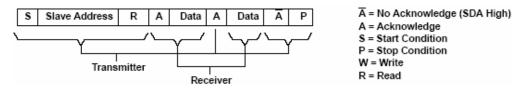

- The master then generates the SCL pulses and transmits the 7-bit address and the *read/write direction bit* R/W on the SDA line. During all transmissions, the master ensures that data is *valid*. A *valid data condition* requires the SDA line to be stable during the entire high period of the clock pulse (see Figure 27). All devices recognize the address sent by the master and compare it to their internal fixed addresses. Only the slave device with a matching address generates an *acknowledge* (see Figure 28) by pulling the SDA line low during the entire high period of the ninth SCL cycle. On detecting this acknowledge, the master knows that a communication link with a slave has been established.

### **Programming (continued)**

- The master generates further SCL cycles to either *transmit* data to the slave (R/W bit 0) or *receive* data from the slave (R/W bit 1). In either case, the receiver needs to acknowledge the data sent by the *transmitter*. So an acknowledge signal can either be generated by the master or by the slave, depending on which one is the receiver. The 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long as necessary (See Figure 29).

- To signal the end of the data transfer, the master generates a *stop condition* by pulling the SDA line from low to high while the SCL line is high (see Figure 29). This releases the bus and stops the communication link with the addressed slave. All I<sup>2</sup>C compatible devices must recognize the stop condition. Upon the receipt of a *stop condition*, all devices know that the bus is released, and they wait for a *start condition* followed by a matching address.

Figure 27. I<sup>2</sup>C Bit Transfer

Figure 28. I<sup>2</sup>C Acknowledge

Figure 29. I<sup>2</sup>C Address And Data Cycles

Copyright © 2009–2017, Texas Instruments Incorporated

### **Programming (continued)**

During a read cycle, the slave receiver will acknowledge the initial address byte if it decodes the address as its address. Following this initial acknowledge by the slave, the master device becomes a receiver and acknowledges data bytes sent by the slave. When the master has received all of the requested data bytes from the slave, the not acknowledge (A) condition is initiated by the master by keeping the SDA signal high just before it asserts the stop (P) condition. This sequence terminates a read cycle as shown in Figure 30 and Figure 31. See Example – Reading from the SN75DP139 section for more information.

Figure 30. I<sup>2</sup>C Read Cycle

Figure 31. Multiple Byte Read Transfer

#### 7.5.3 Slave Address

Both SDA and SCL must be connected to a positive supply voltage via a pull-up resistor. These resistors should comply with the  $I^2C$  specification that ranges from  $2k\Omega$  to  $19k\Omega$ . When the bus is free, both lines are high. The address byte is the first byte received following the START condition from the master device. The 7-bit address is factory preset to 1000000. Table 3 lists the calls that the SN75DP139 will respond to.

Table 3. SN75DP139 Slave Address

|                | Read/Write Bit |       |       |       |       |       |                |

|----------------|----------------|-------|-------|-------|-------|-------|----------------|

| Bit 7<br>(MSB) | Bit 6          | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(R/W) |

| 1              | 0              | 0     | 0     | 0     | 0     | 0     | 1              |

### 7.5.3.1 Sink Port Selection Register And Source Plug-In Status Register Description (Sub-Address)

The SN75DP139 operates using a multiple byte transfer protocol similar to Figure 31. The internal memory of the SN75DP139 contains the phrase "DP-HDMI ADAPTOR<EOT>" converted to ASCII characters. The internal memory address registers and the value of each can be found in Table 4.

During a read cycle, the SN75DP139 will send the data in its selected sub-address in a single transfer to the master device requesting the information. See the *Example – Reading from the SN75DP139* section of this document for the proper procedure on reading from the SN75DP139.

Table 4. SN75DP139 Sink Port And Source Plug-In Status Registers Selection

| Address | 0x00 | 0x01 | 0x02 | 0x03 | 0x04 | 0x05 | 0x06 | 0x07 | 0x08 | 0x09 | 0x0A | 0x0B | 0x0C | 0x0D | 0x0E | 0x0F | 0x10 |

|---------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Data    | 44   | 50   | 2D   | 48   | 44   | 4D   | 49   | 20   | 41   | 44   | 41   | 50   | 54   | 4F   | 52   | 04   | FF   |

Product Folder Links: SN75DP139

### 7.5.3.2 Example – Reading From The SN75DP139:

The read operation consists of several steps. The I<sup>2</sup>C master begins the communication with the transmission of the start sequence followed by the slave address of the SN75DP139 and logic address of 00h. The SN75DP139 will acknowledge it's presence to the master and begin to transmit the contents of the memory registers. After each byte is transferred the SN75DP139 will wait for either an acknowledge (ACK) or a not-acknowledge (NACK) from the master. If an ACK is received the next byte of data will be transmitted. If a NACK is received the data transmission sequence is expected to end and the master should send the stop command.

The SN75DP139 will continue to send data as long as the master continues to acknowledge each byte transmission. If an ACK is received after the transmission of byte 0x0F the SN75DP139 will transmit byte 0x10 and continue to transmit byte 0x10 for all further ACK's until a NACK is received.

The SN75DP139 also supports an accelerated read mode where steps 1-6 can be skipped.

#### SN75DP139 Read Phase

| Step 1                          | 0 |

|---------------------------------|---|

| I <sup>2</sup> C Start (Master) | S |

| Step 2                                          | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------------------------------------------------|---|---|---|---|---|---|---|---|

| I <sup>2</sup> C General Address Write (Master) | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Step 3                               | 9 |

|--------------------------------------|---|

| I <sup>2</sup> C Acknowledge (Slave) | Α |

| Step 4                                  | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------------------------------|---|---|---|---|---|---|---|---|

| I <sup>2</sup> C Logic Address (Master) | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| Step 5                               | 9 |

|--------------------------------------|---|

| I <sup>2</sup> C Acknowledge (Slave) | Α |

| Step 6                         | 0 |

|--------------------------------|---|

| I <sup>2</sup> C Stop (Master) | Р |

| Step 7                          | 0 |

|---------------------------------|---|

| I <sup>2</sup> C Start (Master) | S |

| Step 8                                         | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------------------------------------------|---|---|---|---|---|---|---|---|

| I <sup>2</sup> C General Address Read (Master) | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| Step 9                               | 9 |

|--------------------------------------|---|

| I <sup>2</sup> C Acknowledge (Slave) | Α |

| Step 10                            | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------------------------------------|------|------|------|------|------|------|------|------|

| I <sup>2</sup> C Read Data (Slave) | Data |

Where Data is determined by the Logic values Contained in the Sink Port Register

| Step 11                                   | 9 |

|-------------------------------------------|---|

| I <sup>2</sup> C Not-Acknowledge (Master) | X |

Product Folder Links: SN75DP139

Where X is an A (Acknowledge) or  $\overline{A}$  (Not-Acknowledge) An A causes the pointer to increment and step 10 is repeated. An  $\overline{A}$  causes the slave to stop transmitting and proceeds to step 12.

| Step 12                        | 0 |

|--------------------------------|---|

| I <sup>2</sup> C Stop (Master) | Р |

Submit Documentation Feedback

Copyright © 2009–2017, Texas Instruments Incorporated

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The typical application for the SN75DP139 is to translate from DP++ to TMDS, and thus expand the connectivity for any DP++ source to HDMI 1.4b and DVI sinks. This can be clearly explained when you have the SN75DP139 in a dongle connected to the DP++ source.

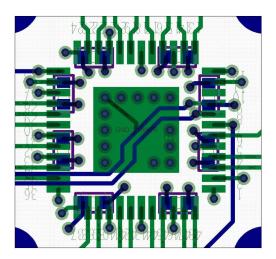

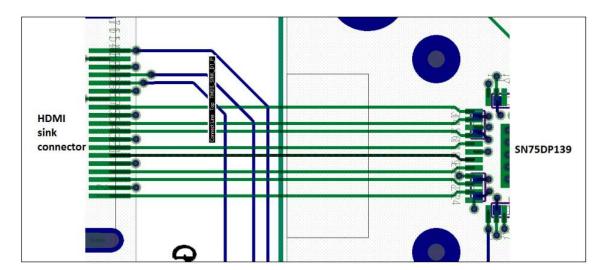

## 8.2 Typical Application

GPU - Graphics Processing Unit DP++ - Dual-Mode DisplayPort

TMDS - Transition-Minimized Differential Signaling

DVI - Digital Visual Interface

HDMI - High Definition Multimedia Interface

Figure 32. Typical Application

#### 8.2.1 Design Requirements

| DESIGN PARAMETERS                                    | VALUE          |

|------------------------------------------------------|----------------|

| VDD Main Power Supply                                | 3.0 - 3.6 V    |

| Main Link Peak-to-Peak AC Input Differential Voltage | 0.15 - 1.2 V   |

| TMDS Output Termination Voltage                      | 3.0 - 3.6 V    |

| TMDS Output Swing Voltage Bias Resistor              | 3.65 - 4.02 kΩ |

### 8.2.2 Detailed Design Procedure

### 8.2.2.1 DVI Application

In DVI application case, it is recommended that between the SN75DP139 TMDS outputs (OUT\_Dx) and a through hole DVI connector that a series resistor placeholder is incorporated. This could help in case if there are signal integrity issues as well as help pass system level compliance.

Product Folder Links: SN75DP139

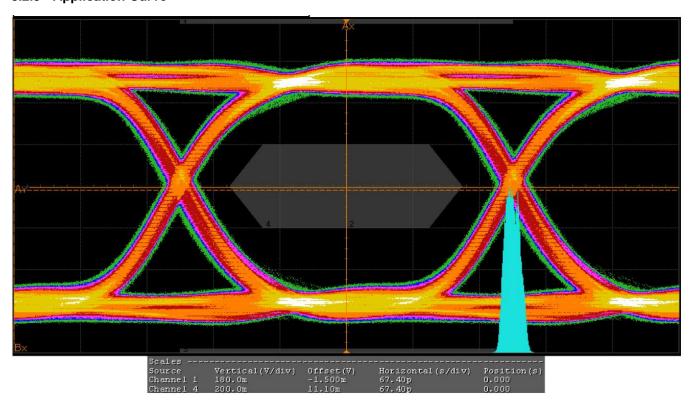

## 8.2.3 Application Curve

Figure 33. Data Jitter

## 9 Power Supply Recommendations

Use a VCC power rail able to supply 110 mA for the SN75DP139, Place four 1 uF, two 0.1 uF and two 0.01 uF capacitors under the SN75DP139 and close to the VCC pins, all connecter in parallel between VCC and GND.

### 10 Layout

## 10.1 Layout Guidelines

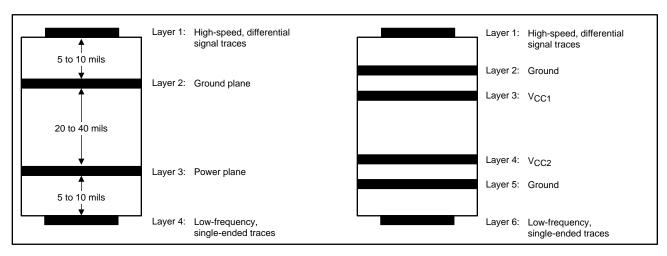

#### 10.1.1 Layer Stack

Figure 34. Recommended 4- or 6- Layer (0.062") Stack for a Receiver PCB Design

Routing the high-speed differential signal traces on the top layer avoids the use of vias (and the introduction of their inductances) and allows for clean interconnects from the DisplayPort connectors to the repeater inputs and from the repeater output to the subsequent receiver circuit.

Placing a solid ground plane next to the high-speed signal layer establishes controlled impedance for transmission line interconnects and provides an excellent low-inductance path for the return current flow.

Placing the power plane next to the ground plane creates additional high-frequency bypass capacitance.

Routing the fast-edged control signals on the bottom layer by prevents them from cross-talking into the high-speed signal traces and minimizes EMI.

If the receiver requires a supply voltage different from the one of the repeater, add a second power/ground plane system to the stack to keep it symmetrical. This makes the stack mechanically stable and prevents it from warping. Also, the power and ground plane of each power system can be placed closer together, thus increasing the high-frequency bypass capacitance significantly. Finally, a second power/ground system provides added isolation between the signal layers.

#### 10.1.2 Differential Traces

Guidelines for routing PCB traces are necessary when trying to maintain signal integrity and lower EMI. Although there seems to be an endless number of precautions to be taken, this section provides only a few main recommendations as layout guidance.

- 1. Reduce intra-pair skew in a differential trace by introducing small meandering corrections at the point of mismatch.